AS1109 Data Sheet

## Constant-Current, 8-Bit LED Driver with Diagnostics

## 1 General Description

The AS1109 is designed to drive up to 8 LEDs through a fast serial interface and features 8 output constant current drivers and an on-chip diagnostic read-back function.

The high clock-frequency (up to 50MHz), adjustable output current, and flexible serial interface makes the device perfectly suited for high-volume transmission applications.

Output current is adjustable (up to 100mA/channel) using an external resistor (REXT).

The serial interface with Schmitt trigger inputs includes an integrated shift register. Additionally, an internal data register stores the currently displayed data.

The device features integrated diagnostics for overtemperature, open-LED, and shorted-LED conditions. Integrated registers store global fault status information during load as well as the detailed temperature/open-LED/shorted-LED diagnostics results.

The AS1109 also features a low-current diagnostic mode to minimize display flicker during fault testing.

With an operating temperature range from -40 to +125°C the AS1109 is also ideal for industrial applications.

The AS1109 is available in a 16-pin SOIC-150, a 16-pin QFN (4x4mm) and the 16-pin SSOP-150 package.

## 2 Key Features

- 8 Constant-Current Output Channels

- Excellent Output Current Accuracy

- Between Channels: ±2%

- Between AS1109 Devices: ±2%

- Output Current Per Channel: 0.5 to 100mA

- Controlled In-Rush Current

- Over-Temperature, Open-LED, Shorted-LED Diagnostics Functions

- Low-Current Test Mode

- Global Fault Monitoring

- Low Shutdown Mode Current: 3µA

- Fast Serial Interface: up to 50MHz

- Cascaded Configuration

- Fast Output Drivers Suitable for PWM

- 16-pin SOIC-150, 16-pin QFN (4x4mm) and 16-pin SSOP-150 Package

## 3 Applications

The device is ideal for fixed- or slow-rolling displays using static or multiplexed LED matrix and dimming functions, large LED matrix displays, mixed LED display and switch monitoring, displays in elevators, public transports (underground, trains, buses, taxis, airplanes, etc.), large displays in stadiums and public areas, price indicators in retail stores, promotional panels, bar-graph displays, industrial controller displays, white good panels, emergency light indicators, and traffic signs.

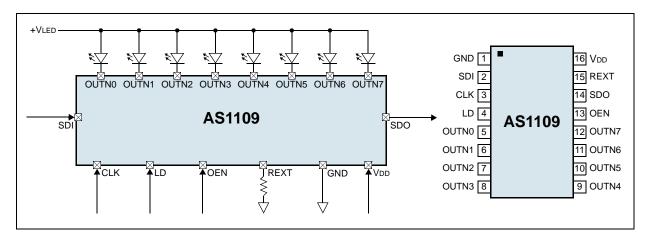

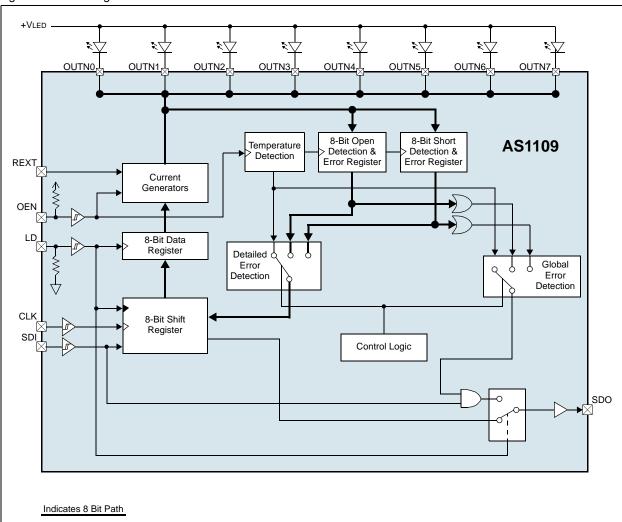

Figure 1. Main Diagram and Pin Assignments

### **Contents**

| 1  | General Description                             | 1    |

|----|-------------------------------------------------|------|

| 2  | Key Features                                    | 1    |

| 3  | Applications                                    | 1    |

| 4  | Pinout                                          | 3    |

|    | Pin Assignments                                 | 3    |

|    | Pin Descriptions                                |      |

| 5  | Absolute Maximum Ratings                        |      |

|    | Electrical Characteristics                      |      |

| Ū  | Switching Characteristics                       |      |

| 7  | Typical Operating Characteristics               |      |

|    | Detailed Description                            |      |

| O  | Serial Interface                                |      |

|    | Timing Diagrams                                 |      |

|    | Error-Detection Mode                            |      |

|    | Global Error Mode                               |      |

|    | Error Detection Functions                       |      |

|    | Open-LED Detection                              |      |

|    | Shorted-LED                                     |      |

|    | Overtemperature                                 |      |

|    | Detailed Error Reports                          |      |

|    | Detailed Temperature Warning Report             |      |

|    | Detailed Open-LED Error Report                  |      |

|    | Detailed Shorted-LED Error Report               | . 15 |

|    | Low-Current Diagnostic Mode                     | 15   |

|    | Shutdown Mode                                   | . 16 |

| 9  | Application Information                         | 17   |

|    | Error Detection                                 | . 17 |

|    | Error Detection On-The-Fly                      | . 17 |

|    | Error Detection with Low-Current Diagnosis Mode | . 17 |

|    | Cascading Devices                               | . 18 |

|    | Constant Current                                | . 19 |

|    | Adjusting Output Current                        | . 19 |

|    | Package Power Dissipation                       | . 19 |

|    | Delayed Outputs                                 | . 19 |

|    | Switching-Noise Reduction                       | . 19 |

|    | Load Supply Voltage                             | . 19 |

| 10 | Package Drawings and Markings                   | 21   |

| 11 | Ordering Information                            | 25   |

## 4 Pinout

## **Pin Assignments**

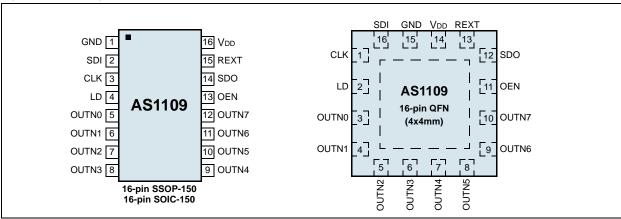

Figure 2. Pin Assignments (Top View)

## **Pin Descriptions**

Table 1. Pin Descriptions

| Pin Nu                             | mber | 5: N     | D. 1.0                                                                                                                                                                                                                                         |  |

|------------------------------------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 16-pin SSOP-150 16-pin QFN (4x4mm) |      | Pin Name | Description                                                                                                                                                                                                                                    |  |

| 1                                  | 15   | GND      | Ground                                                                                                                                                                                                                                         |  |

| 2                                  | 16   | SDI      | Serial Data Input                                                                                                                                                                                                                              |  |

| 3                                  | 1    | CLK      | <b>Serial Data Clock</b> . The rising edge of the CLK signal is used to clock data into and at the falling edge out of the AS1109 shift register. In error mode, the rising edge of the CLK signal is used to switch error modes.              |  |

| 4                                  | 2    | LD       | <b>Serial Data Load.</b> Data is transferred to the data register at the rising edge of this pin.                                                                                                                                              |  |

| 5:12                               | 3:10 | OUTN0:7  | Output Current Drivers. These pins are used as LED drivers or for input sense for diagnostic modes.                                                                                                                                            |  |

| 13                                 | 11   | OEN      | Output Enable. The active-low pin OEN signal can always enable output drivers to sink current independent of the AS1109 mode.  0 = Output drivers are enabled.  1 = Output drivers are disabled.                                               |  |

| 14                                 | 12   | SDO      | Serial Data Output. In normal mode SDO is clocked out 8.5 clock cycles after SDI is clocked in.  In global error detection mode this pin indicates the occurrence of a global error.  0 = Global error mode returned an error.  1 = No errors. |  |

| 15                                 | 13   | REXT     | <b>External Resistor Connection</b> . This pin connects through the external resistor (REXT) to GND, to setup the load current.                                                                                                                |  |

| 16                                 | 14   | VDD      | Positive Supply Voltage                                                                                                                                                                                                                        |  |

# **5 Absolute Maximum Ratings**

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Section 6 Electrical Characteristics on page 5 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parame                   | eter            | Min                    | Max                     | Units | Comments                                                                                                                                                                                                                                                                            |

|--------------------------|-----------------|------------------------|-------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD to G                 | SND             | 0                      | 7                       | V     |                                                                                                                                                                                                                                                                                     |

| Input Vol                | tage            | -0.4                   | V <sub>DD</sub><br>+0.4 | V     |                                                                                                                                                                                                                                                                                     |

| Output Vo                | oltage          | -0.4                   | 15                      | V     |                                                                                                                                                                                                                                                                                     |

| GND Pin C                | Current         |                        | 1000                    | mA    |                                                                                                                                                                                                                                                                                     |

|                          |                 |                        | 83                      | °C/W  | on PCB, 16-pin SOIC-150 package                                                                                                                                                                                                                                                     |

| Thermal Resis            | tance ΘJA       | 1                      | 13                      | °C/W  | on PCB, 16-pin SSOP-150 package                                                                                                                                                                                                                                                     |

|                          |                 | 32                     |                         | °C/W  | on PCB, 16-pin QFN (4x4mm) package                                                                                                                                                                                                                                                  |

| Operating Tempe          | rature Range    | -40                    | +85                     | °C    | Device fully functional up to 125°C                                                                                                                                                                                                                                                 |

| Storage Tem              | perature        | -55                    | 150                     | °C    |                                                                                                                                                                                                                                                                                     |

| Humid                    | ity             | 5                      | 86                      | %     | Non-condensing                                                                                                                                                                                                                                                                      |

| Electrostatic            | Digital Outputs |                        | 2000                    | V     | Norm: MIL 833 E method 3015                                                                                                                                                                                                                                                         |

| Discharge                | All Other Pins  |                        | 2000                    | ] V   |                                                                                                                                                                                                                                                                                     |

| Latch-Up Im              | nmunity         | -100 -<br>(INOM x 0.5) | +100 +<br>Inom          | mA    | EIA/JESD78                                                                                                                                                                                                                                                                          |

| Package Body Temperature |                 |                        | +260                    | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020C "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

<sup>\*</sup> Min/max values are load dependent.

## **6 Electrical Characteristics**

VDD = +3.0 to +5.5V, TAMB = -40 to +85°C (unless otherwise specified). Typical values measured at VDD = 5V, TAMB = 25°C.

Table 3. Electrical Characteristics

| Symbol                   | Pa                                                             | arameter                            | Condition                                                                                                                       | Min           | Тур   | Max                   | Unit |  |

|--------------------------|----------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-----------------------|------|--|

| VDD                      | Supply Voltage                                                 |                                     |                                                                                                                                 | 3.0           |       | 5.5                   | V    |  |

| VDS                      | Output Voltage                                                 |                                     | OUTN0:7                                                                                                                         | 0             |       | 15.0                  | V    |  |

| Іоит                     |                                                                |                                     | OUTN0:7, VDD = 5V (see Figure 8)                                                                                                | 0.5           |       | 100                   |      |  |

| Іон                      | Outp                                                           | out Current                         | SDO                                                                                                                             | -1.0          |       |                       | mA   |  |

| lol                      |                                                                |                                     | SDO                                                                                                                             | 1.0           |       |                       |      |  |

| ViH                      | Input Voltage                                                  | High Level                          | CLK, OEN, LD, SDI                                                                                                               | 0.7 x<br>VDD  |       | V <sub>DD</sub> + 0.3 | V    |  |

| VIL                      | input voitage                                                  | Low Level                           | CLN, OLN, ED, 3DI                                                                                                               | -0.3          |       | 0.3 x<br>VDD          |      |  |

| IDS(OFF)                 | Output L                                                       | eakage Current                      | OEN = 1, VDS = 15.0V                                                                                                            |               |       | 0.5                   | μΑ   |  |

| Vol                      | Output                                                         |                                     | IoL = +1.0mA                                                                                                                    |               |       | 0.4                   |      |  |

| Vон                      | Voltage                                                        | SDO                                 | Iон = -1.0mA                                                                                                                    | VDD -<br>0.4V |       |                       | V    |  |

| IAV(LC1)                 | Device-to-De<br>Current from                                   | vice Average Output OUTN0 to OUTN7  | $\begin{aligned} \text{VDS} &= 0.5 \text{V, VDD} = \text{Const.,} \\ \text{REXT} &= 744 \Omega \end{aligned}$                   | 24.5          | 25.26 | 26                    | mA   |  |

| $\Delta \text{IAV(LC1)}$ |                                                                | rent Skew<br>en Channels)           | $\label{eq:VDS} \begin{aligned} \text{Vds} \geq \text{0.5V, Vdd} &= \text{Const.,} \\ \text{Rext} &= 744\Omega \end{aligned}$   |               | ±0.9  | ±3                    | %    |  |

| IAV(LC2)                 | Device-to-Device Average Output<br>Current from OUTN0 to OUTN7 |                                     | $\begin{aligned} \text{VDS} &= 0.6\text{V},  \text{VDD} > 3.3\text{V}, \\ \text{REXT} &= 372\Omega \end{aligned}$               | 49.50         | 50.52 | 51.55                 | mA   |  |

| $\Delta$ lAV(LC2)        | Current Skew<br>(Between Channels)                             |                                     | $\label{eq:VDS} \begin{aligned} \text{VdS} \geq 0.6 \text{V, Vdd} &= \text{Const.,} \\ \text{REXT} &= 372 \Omega \end{aligned}$ |               | ±0.8  | ±2                    | %    |  |

| IAV(LC3)                 | Device-to-De<br>Current from                                   | vice Average Output OUTN0 to OUTN7  | $V_{DS} = 0.8V, V_{DD} = 5.0V,$ $R_{EXT} = 186\Omega$                                                                           | 98            | 101   | 104                   | mA   |  |

| $\Delta$ lAV(LC3)        |                                                                | rent Skew<br>en Channels)           | $\label{eq:Vds} \begin{aligned} \text{Vds} &\geq 0.8 \text{V, Vdd} = \text{Const.,} \\ \text{Rext} &= 186 \Omega \end{aligned}$ |               | ±0.5  | ±2                    | %    |  |

| ILC                      | Low-Currer                                                     | nt Diagnosis Mode                   | VDS = 0.8V, VDD = 5.0V                                                                                                          | 0.4           | 0.6   | 0.8                   | mA   |  |

| IPD                      | Power Dov                                                      | vn Supply Current                   | $V_{DS} = 0.8V, V_{DD} = 5.0V,$<br>$R_{EXT} = 372\Omega, OUTN0:7 = On$                                                          |               | 3     | 20                    | μA   |  |

| %/ΔVDS                   | Output Vo                                                      | it Current vs.<br>oltage Regulation | VDS within 1.0 and 3.0V                                                                                                         |               | ±0.1  |                       | %/V  |  |

| %/∆Vdd                   | Output Current vs.<br>Supply Voltage Regulation                |                                     | VDD within 3.0 and 5.0V                                                                                                         |               | ±1    |                       | %/V  |  |

| RIN(UP)                  | Pullup Resistance                                              |                                     | OEN                                                                                                                             | 250           | 500   | 800                   | kΩ   |  |

| RIN(DOWN)                | Pulldown Resistance                                            |                                     | LD                                                                                                                              | 250           | 500   | 800                   | kΩ   |  |

| VTHL*                    | Open Error Detection Threshold<br>Voltage                      |                                     | No load                                                                                                                         | 0.25          | 0.35  | 0.45                  | V    |  |

| \/ <del></del> *         |                                                                | Detection Threshold                 | VDD = 3.0V, no load                                                                                                             | 1.2           | 1.3   | 1.4                   | V    |  |

| Vтнн                     |                                                                | Voltage                             | VDD = 5.0V, no load                                                                                                             | 2.0           | 2.2   | 2.4                   | _ v  |  |

| Tov1                     | Overtemperature Threshold Flag                                 |                                     |                                                                                                                                 |               | 150   |                       | ∘C   |  |

Table 3. Electrical Characteristics (Continued)

| Symbol    | Parameter         |     | Condition                          | Min | Тур  | Max  | Unit |

|-----------|-------------------|-----|------------------------------------|-----|------|------|------|

| IDD(OFF)0 |                   |     | REXT = Open, OUTN0:7 = Off         |     | 1.3  | 2    |      |

| IDD(OFF)1 |                   | Off | Rext = $744\Omega$ , OUTN0:7 = Off |     | 3.0  | 3.68 |      |

| IDD(OFF)2 |                   | Oii | Rext = $372\Omega$ , OUTN0:7 = Off |     | 4.7  | 5.37 |      |

| IDD(OFF)3 | Supply<br>Current |     | Rext = $186\Omega$ , OUTN0:7 = Off |     | 8.1  | 8.73 | mA   |

| IDD(ON)1  | 2                 |     | REXT = $744\Omega$ , OUTN0:7 = On  |     | 4.5  | 5    |      |

| IDD(ON)2  |                   | On  | Rext = $372\Omega$ , OUTN0:7 = On  |     | 7.5  | 8    |      |

| IDD(ON)3  |                   |     | Rext = $186\Omega$ , OUTN0:7 = On  |     | 13.7 | 15   |      |

## **Switching Characteristics**

VDD = 3.0 to 5.5V, VDS = 0.8V, VIH = VDD, VIL = GND,  $REXT = 372\Omega$ , VLOAD = 4.0V,  $RLOAD = 64\Omega$ , CLOAD = 10pF; guaranteed by design.

Table 4. Switching Characteristics

| Symbol      | Parameter                                   | Conditions                                                                                         | Min  | Тур  | Max | Unit |

|-------------|---------------------------------------------|----------------------------------------------------------------------------------------------------|------|------|-----|------|

| tP1         | Propagation Delay Time                      | CLK - SDO                                                                                          |      | 5    | 10  |      |

| tP2         | Propagation Delay Time (Without             | LD - OUTNn                                                                                         |      | 100  | 200 | ns   |

| tP3         | Staggered Output Delay)                     | OEN - OUTNn                                                                                        |      | 100  | 200 |      |

| tP4         | Propagation Delay Time                      |                                                                                                    |      |      | 10  | ns   |

| tW(CLK)     |                                             | CLK                                                                                                | 15   |      |     |      |

| tW(L)       | Pulse Width                                 | LD                                                                                                 | 15   |      |     | ns   |

| tW(OE)      |                                             | OEN (@Iout < 60mA)                                                                                 | 200  |      |     |      |

| tr *        | Maximum CLK Rise Time                       |                                                                                                    |      |      | 500 | ns   |

| tF *        | Maximum CLK Fall Time                       |                                                                                                    |      |      | 500 | ns   |

| tor         | Output Rise Time of Vout (Turn Off)         |                                                                                                    |      | 100  | 200 | ns   |

| tor         | Output Fall Time of Vo∪T (Turn On)          |                                                                                                    |      | 100  | 300 | ns   |

| tsu(D)      | Setup Time for SDI                          |                                                                                                    | 5    |      |     | ns   |

| tH(D)       | Hold Time for SDI                           |                                                                                                    | 5    |      |     | ns   |

| tsu(L)      | Setup Time for LD                           |                                                                                                    | 5    |      |     | ns   |

| tH(L)       | Hold Time for LD                            |                                                                                                    | 5    |      |     | ns   |

| ttesting    | Minimum OEN Time for Error Detection        |                                                                                                    | 2000 |      |     | ns   |

| tSTAG       | Staggered Output Delay                      |                                                                                                    |      | 20   | 40  | ns   |

| tsu(oe)     | Output Enable Setup Time                    |                                                                                                    | 20   |      |     | ns   |

| tgsw(error) | Global Error Switching Setup Time           |                                                                                                    | 10   |      |     | ns   |

| tsu(error)  | Global Error Detection Setup Time           |                                                                                                    | 10   |      |     | ns   |

| tP(I/O)     | Propagation Delay Global Error Flag         |                                                                                                    |      |      | 5   | ns   |

| tsw(error)  | Switching Time Global Error Flag            |                                                                                                    |      |      | 10  | ns   |

| fclk        | Maximum Clock Frequency (Cascade Operation) |                                                                                                    | 30   | 50   |     | MHz  |

| tP3,ON      | Low-Current Test Mode                       | Turn ON                                                                                            |      | 3    | 5   | μs   |

| tTP3,OFF    | Propagation Delay Time                      | Turn OFF                                                                                           |      | 0.05 | 0.1 | μs   |

| tREXT2,1    | External Resistor Reaction Time             | Change from REXT1 = $372\Omega$ ,<br>IOUT1 = $50.52$ mA to REXT2 = $37.2$ k $\Omega$ , IOUT2 < 1mA |      | 0.5  | 1   | μs   |

| tREXT2,1    | External Resistor Reaction Time             | Change from REXT1 = $37.2k\Omega$ ,<br>IOUT1 = $0.5$ mA to REXT2 = $372\Omega$ , IOUT2 > $25$ mA   |      | 0.5  | 1   | μs   |

<sup>\*</sup> If multiple AS1109 devices are cascaded and tr or tr is large, it may be critical to achieve the timing required for data transfer between two cascaded LED drivers.

\*

## 7 Typical Operating Characteristics

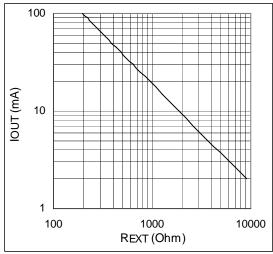

Figure 3. Output Current vs. REXT, VDD = 5V; VOUT = 0.8V, TAMB = 25°C

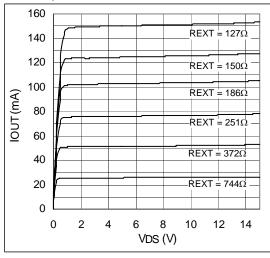

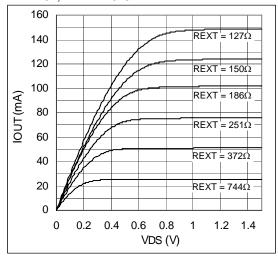

Figure 5. Output Current vs. VDS; VDD = 5V, TAMB = 25°C

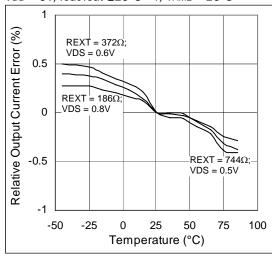

Figure 7. Relative IOUT Error vs. Temperature VDD = 5V, Iout/Iout@25°C - 1, TAMB = 25°C

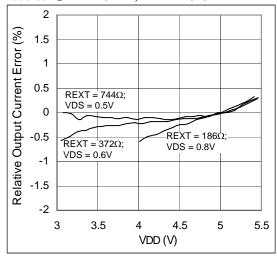

Figure 4. Relative Output Current Error vs. VDD, Iout/Iout@VDD = 5V - 1, TAMB = 25°C

Figure 6. Output Current vs. VDS; VDD = 5V, TAMB = 25°C

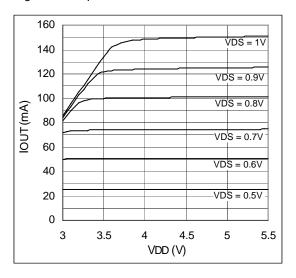

Figure 8. Output Current vs. VDD

## 8 Detailed Description

The AS1109 is designed to drive up to 8 LEDs through a fast serial interface and 8 constant-current output drivers. Furthermore, the AS1109 provides diagnostics for detecting open- or shorted-LEDs, as well as over-temperature conditions for LED display systems, especially LED traffic sign applications.

The AS1109 contains an 8-bit shift register and an 8-bit data register, which convert serial input data into parallel output format. At AS1109 output stages, eight regulated current sinks are designed to provide uniform and constant current with excellent matching between ports for driving LEDs within a wide range of forward voltage variations. External output current is adjustable from 0.5 to 100mA using an external resistor for flexibility in controlling the brightness intensity of LEDs. The AS1109 guarantees to endure 15V maximum at the outputs.

The serial interface is capable of operating at a minimum of 30 MHz, satisfying the requirements of high-volume data transmission.

Using a multiplexed input/output technique, the AS1109 adds additional functionality to pins SDO, LD and OEN. These pins provide highly useful functions (open- and shorted-LED detection, over-temperature detection), thus reducing pin count. Over-temperature detection will work on-the-run, whereas the open- and shorted-LED detection can be used on-the-run or in low-current diagnostic mode (see page 15).

Figure 9. Block Diagram

### **Serial Interface**

Data accesses are made serially via pins SDI and SDO. At each CLK rising edge, the signal present at pin SDI is shifted into the first bit of the internal shift register and the other bits are shifted ahead of the first bit. The MSB is the first bit to be clocked in. In error-detection mode the shift register will latch-in the corresponding error data of temperature-, open-, and short-error register with each falling edge of LD.

The 8-bit data register will latch the data of the shift register at each rising edge of LD. This data is then used to drive the current generator output drivers to switch on the corresponding LEDs as OEN goes low.

### **Timing Diagrams**

This section contains timing diagrams referenced in other sections of this data sheet.

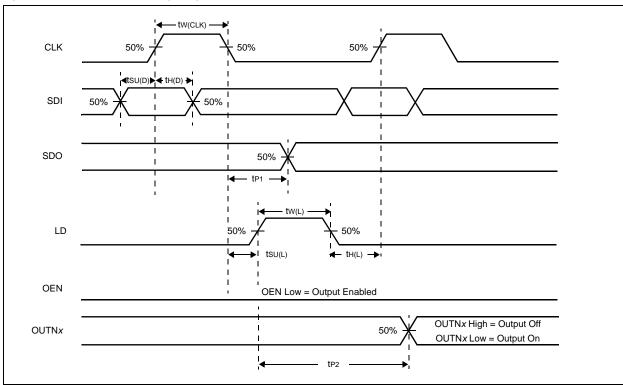

Figure 10. Normal Mode Timing Diagram

Figure 11. Output Delay Timing Diagram

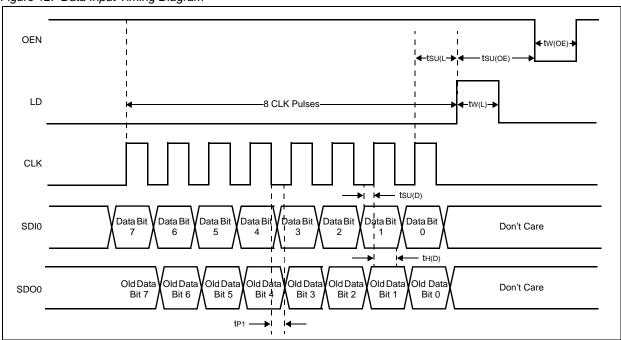

Figure 12. Data Input Timing Diagram

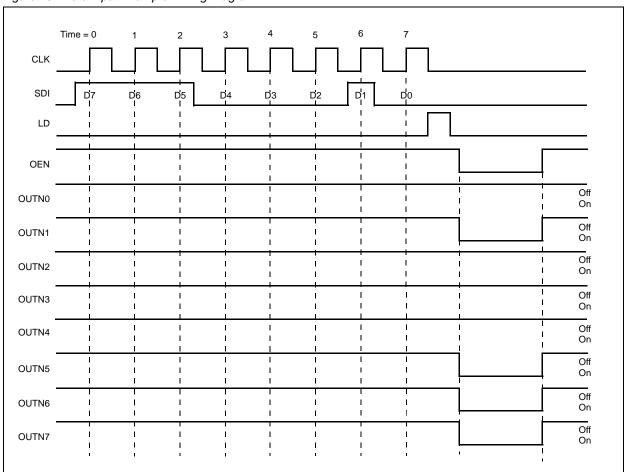

Figure 13. Data Input Example Timing Diagram

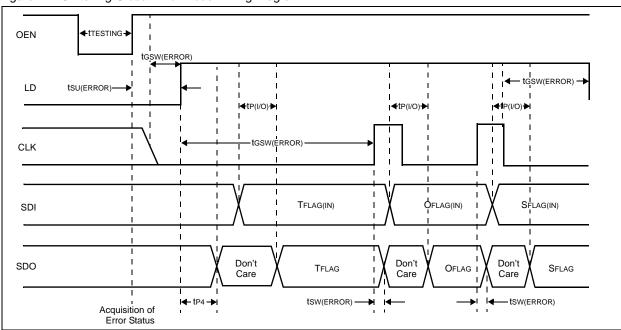

Figure 14. Switching Global Error Mode Timing Diagram

#### **Error-Detection Mode**

Acquisition of the error status occurs at the rising edge of OEN. Error-detection mode is started on the rising edge of LD when OEN is high. The CLK signal must be low when entering error detection mode. Error detection for open- and shorted-LEDs can only be performed for LEDs that are switched on during test time. To switch between error-detection modes clock pulses are needed (see Table 5).

Note: To test all LEDs, a test pattern that turns on all LEDs must be input to the AS1109.

#### **Global Error Mode**

Global error mode is entered when error-detection mode is started. Clock pulses during this period are used to select between temperature, open-LED, and shorted-LED tests, as well as low-current diagnostic mode and shutdown mode (see Table 5). In global error mode, an error flag (TFLAG, OFLAG, SFLAG) is delivered to pin SDO if any errors are encountered.

Table 5. Global Error Mode Selections

| Clock<br>Pulses | Output Port                              | Error-Detection Mode          | Global Error Flag/Shutdown Condition          |

|-----------------|------------------------------------------|-------------------------------|-----------------------------------------------|

| 0               | ()   Don't Care   State States           |                               | TFLAG = SDO = 1: No over-temperature warning. |

|                 | Boilt Galo                               | Detection                     | TFLAG = SDO = 0: Over-temperature warning.    |

| 4               | 1   Enabled   ()non   El) Detection      |                               | OFLAG = SDO = 1: No open-LED error.           |

| 1               |                                          |                               | OFLAG = SDO = 0: Open-LED error.              |

| 2               | Enabled                                  | Enghand Charted LED Detection | SFLAG = SDO = 1: No shorted-LED error.        |

|                 | 2 Enabled Shorted-LED Detection          |                               | SFLAG = SDO = 0: Shorted-LED error.           |

| 3               | 3 Don't Care Low-Current Diagnostic Mode |                               |                                               |

| 4               | Don't Care                               | Shutdown Mode                 | SDI = 1: Wakeup<br>SDI = 0: Shutdown          |

Note: For a valid result SDI must be 1 for the first device.

If there are multiple AS1109s in a chain, the error flag will be gated through all devices. To get a valid result at the end of the chain, a logic 1 must be applied to the SDI input of the first device of the chain. If one device produces an error this error will show up after  $n^*tP(I/O) + tsW(ERROR)$  at pin SDO of the last device in the chain. This means it is not possible to identify which device in the chain produced the error. Therefore, if a global error occurs, the detailed error report can be run to identify which AS1109, or LED produced the error.

Note: When no error has occurred, the detailed error report can be skipped, setting LD and subsequently OEN low.

#### **Error Detection Functions**

#### **Open-LED Detection**

The AS1109 open-LED detection is based on the comparison between VDS and VTHL. The open LED status is aquired at the rising edge of OEN and stored internally. While detecting open-LEDs the output port must be turned on. Open LED detection can be started with 1 clock pulse during error detection mode while the output port is turned on.

Note: LEDs which are turned off at test time cannot be tested.

Table 6. Open LED Detection Modes

| Output Port State | Effective Output<br>Point Conditions | Detected Open-LED<br>Error Status Code | Meaning      |

|-------------------|--------------------------------------|----------------------------------------|--------------|

| On                | VDS < VTHL                           | 0                                      | Open Circuit |

| On                | VDS > VTHL                           | 1                                      | Normal       |

#### Shorted-LED

The AS1109 shorted-LED detection is based on the comparison between VDS and VTHH. The shortened LED status is aquired at the rising edge of OEN and stored internally. While detecting shorted-LEDs the output port must be turned on. Shorted-LED detection can be started with 2 clock pulses during error detection mode while the output port is turned on.

For valid results, the voltage at OUTN0:OUTN7 must be lower then VTHH under low-current diagnostic mode operating conditions. This can be achieved by reducing the VLED voltage or by adding additional diodes, resistors or LED's.

Note: LEDs which are turned off at test time cannot be tested.

Table 7. Shorted LED Detection Modes

| Output Port State | Effective Output<br>Point Conditions | Detected Shorted-LED<br>Error Status Code | Meaning       |

|-------------------|--------------------------------------|-------------------------------------------|---------------|

| On                | VDS > VTHH                           | 0                                         | Short Circuit |

| On                | VDS < VTHH                           | 1                                         | Normal        |

#### Overtemperature

Thermal protection for the AS1109 is provided by continuously monitoring the device's core temperature. The overtemperature status is aquired at the rising edge of OEN and stored internally.

Table 8. Overtemperature Modes

| Output Port State | Effective Output<br>Point Conditions | Detected Overtemperature<br>Status Code | Meaning                      |

|-------------------|--------------------------------------|-----------------------------------------|------------------------------|

| Don't Care        | Temperature > Tov1                   | 0                                       | Overtemperature<br>Condition |

| Don't Care        | Temperature < Tov1                   | 1                                       | Normal                       |

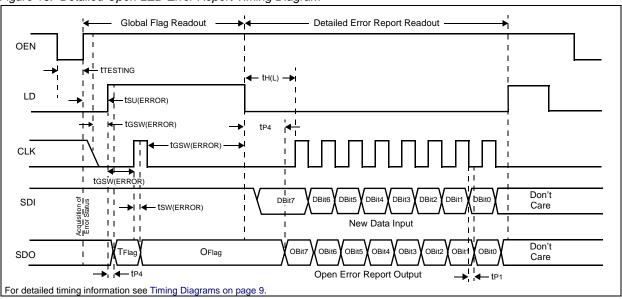

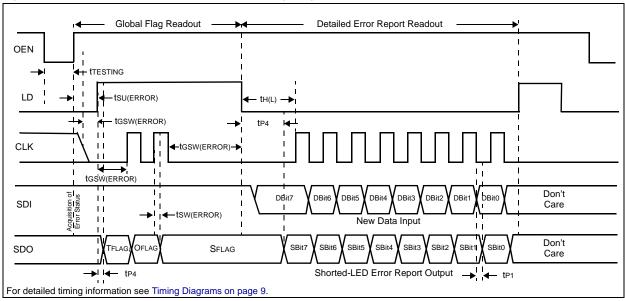

### **Detailed Error Reports**

The detailed error report can be read out after global error mode has been run. On the falling edge of LD, the detailed error report of the selected test is latched into the shift register and can be clocked out with n\*8 clock cycles (n is the number of AS1109s in a chain) via pin SDO. At the same time new data can be written into the shift register, which will load on the next rising edge of pin LD. This data will show at the output drivers, at the falling edge of OEN.

#### **Detailed Temperature Warning Report**

The detailed temperature warning report can be read out immediately after global error mode has been run. Bit0 of the 8bit data word represents the temperature flag of the chip.

Global Flag Readout Detailed Error Report Readout OEN tH(L) tGSW(ERROR) LD t(SU)ERROR CLK Don't DBit4 SDI Care New Data Input Don't **TFLAG** SDO Undefined Care Temperature Error Report Output ◆ tP4

Figure 15. Detailed Temperature Warning Report Timing Diagram

#### Detailed Temperature Warning Report Example

For detailed timing information see Timing Diagrams on page 9.

Consider a case where five AS1109s are cascaded in one chain. The detailed error report lists the temperatures for each device in the chain:

In this case, IC4 is overheated and will generate a global error, and therefore 5\*8 clock cycles are needed to write out the detailed temperature warning report, and optionally read in new data. The detailed temperature warning report would look like this:

#### XXXXXXX1 XXXXXXX1 XXXXXXX1 XXXXXXX0 XXXXXXX1

The 0 in the detailed temperature warning report indicates that IC4 is the device with the over-temperature condition.

Note: In an actual report there are no spaces in the output.

#### **Detailed Open-LED Error Report**

The detailed open-LED error report can be read out immediately after global error mode has been run.

Figure 16. Detailed Open-LED Error Report Timing Diagram

#### Detailed Open-LED Error Report Example

Consider a case where five AS1109s are cascaded in one chain. A 1 indicates a LED is on, a 0 indicates a LED is off, and an X indicates an open LED. The open-LED test is only applied to LEDs that are turned on. This test is used with a test pattern where all LEDs are on at test time.

IC1:[11111111] IC2:[111XX111] IC3:[11111111] IC4:[1X111111] IC5:[11111111]

IC2 has two open LEDs and IC4 has one open LED switched on due to input. 5\*8 clock cycles are needed to write the entire error code out. The detailed error report would look like this:

Comparing this report with the input data indicates that IC2 is the device with two open LEDs at position 4 and 5 and IC4 with an open LED at second position. For such a test it is recommended to enter low-current diagnostic mode first (see Low-Current Diagnostic Mode on page 15) to reduce onscreen flickering.

Note: In an actual report there are no spaces in the output.

LEDs turned off during test time cannot be tested.

#### **Detailed Shorted-LED Error Report**

The detailed shorted-LED error report can be read out immediately after global error mode has been run (see Global Error Mode on page 11).

Figure 17. Detailed Shorted-LED Error Report Timing Diagram

#### Detailed Shorted-LED Error Report Example

Consider a case where five AS1109s are cascaded in one chain. A 1 indicates a LED is on, a 0 indicates a LED is off, and an X indicates a shorted LED. This test is used with a test pattern where all LEDs are on at test time. Additionally, this test should be run after starting low-current diagnostic mode (see Low-Current Diagnostic Mode on page 15).

IC1:[11111XX1] IC2:[11111111] IC3:[11111111] IC4:[111X1111] IC5:[11111111]

IC2 has two shorted LEDs and IC4 has one shorted LED switched on due to input. 5\*8 clock cycles are needed to write the entire error code out. The detailed error report would look like this:

Showing IC1 as the device with two shorted LEDs at position 6 and 7, and IC4 with one shorted LED at position 4.

Note: In an actual report there are no spaces in the output. LEDs turned off during test time cannot be tested.

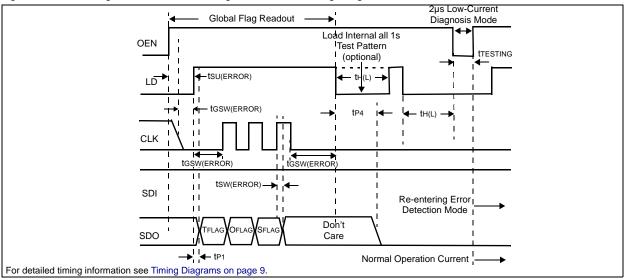

#### **Low-Current Diagnostic Mode**

To run the open- or shorted-LED test, a test pattern must be used that will turn on each LED to be tested. This test pattern will cause a short flicker on the screen while the test is being performed. The low-current diagnostic mode can be initiated prior to running a detailed error report to reduce this on-screen flickering.

**Note:** Normally, displays using such a diagnosis mode require additional cables, resistors, and other components to reduce the current. The AS1109 has this current-reduction capability built-in, thereby minimizing the number of external components required.

Low-current diagnostic mode can be initiated via 3 clock pulses during error-detection mode. After the falling edge of LD, a test pattern displaying all 1s can be written to the shift register which will be used for the next error-detection test.

On the next falling edge of OEN, current is reduced to ILC. With the next rising edge of OEN the current will immediately increase to normal levels and the detailed error report can be read out entering error-detection mode.

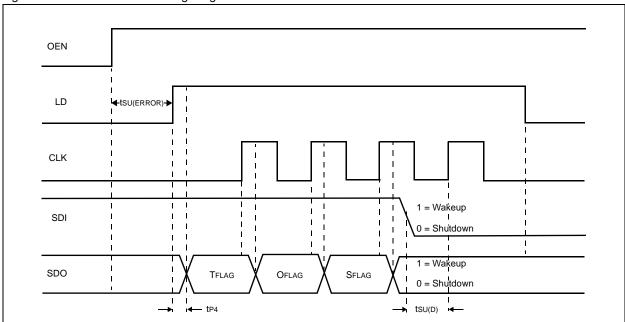

Figure 18. Switching into Low-Current Diagnostic Mode Timing Diagram

#### **Shutdown Mode**

The AS1109 features a shutdown mode which can be entered via 4 clock pulses during error-detection mode. To enable the shutdown mode a 0 must be placed at SDI after the rising edge of the 3rd clock pulse.

To disable shutdown mode a 1 must be placed at SDI after the 3rd clock pulse. The shutdown/wakeup information will be latched through if multiple AS1109 devices are in a chain. At the rising edge of the 4th clock pulse the shutdown bit will be read out and the AS1109 will shutdown or wakeup.

Note: In shutdown mode the supply current drops down to typically  $3\mu A$ .

Figure 19. Shutdown Mode Timing Diagram

GEF = Global Error Flag

## 9 Application Information

#### **Error Detection**

Current

The AS1109 features two types of error detection. The error detection can be used on-the-fly, for active LEDs, without any delay, or by entering into low-current diagnosis mode.

#### **Error Detection On-The-Fly**

Error detection on-the-fly will output the status of active LEDs during operation. Without choosing an error mode this will output the temperature flag at every input/output cycle. Triggering one clock pulse for open or two clock pulses for short detection during error detection mode outputs the detailed open- or short-error report with the next input/output cycle (see Figure 20). LEDs that are turned off cannot be tested and their digits at the error output must be ignored.

Data1 Data3 Display Data2 SDI Data2 Data3 Data4 T/O or S Error Code T/O or S Error Code T/O or S Error Code SDO Data0 Data1 Data2 Clock for Error Clock for Error Mode 0x/1x/2x Mode 0x/1x/2x  $0.0000001024 ext{x}$ Æ Rising Edge of OEN Rising Edge of OEN OFN Acquisition of Error Status Acquisition of Error Status IFalling Edge of LD; Error Register is Falling Edge of LD; Error Register is LD copied into Shift Register copied into Shift Register

Figure 20. Normal Operation with Error Detection During Operation – 128 Cascaded AS1109s

#### **Error Detection with Low-Current Diagnosis Mode**

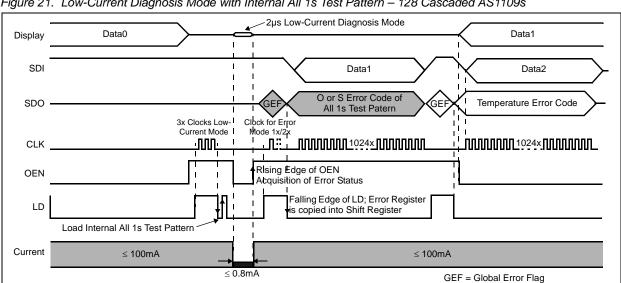

This unique feature of the AS1109 uses an internal all 1s test pattern for a flicker free diagnosis of all LEDs. This error detection mode can be started anytime, and does not require any SDI input (see Figure 21).

≤ 100mA

Figure 21. Low-Current Diagnosis Mode with Internal All 1s Test Pattern – 128 Cascaded AS1109s

Low-current diagnosis mode is started with 3 clock pulses during error detection mode. After the three pulses of CLK, a pulse of LD loads the internal all 1s test pattern. Then OEN should be enabled for 2µs for testing. With the rising edge of OEN the test of the LEDs is stopped and while LD is high the desired error mode can be selected with the corresponding clock pulses.

With the next data input the detailed error code will be clocked out at SDO.

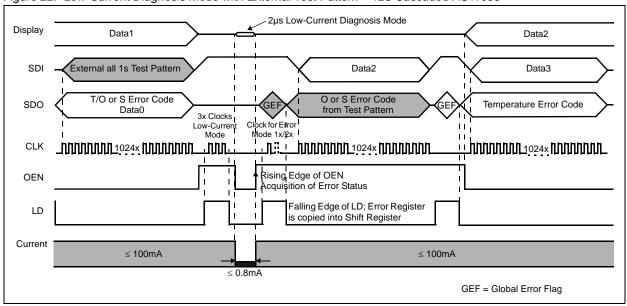

**Note:** See Figure 22 for the use of an external test pattern.

Figure 22. Low-Current Diagnosis Mode with External Test Pattern - 128 Cascaded AS1109s

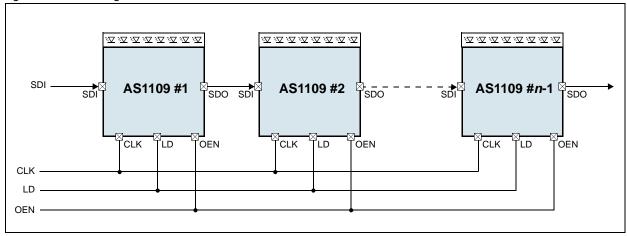

### **Cascading Devices**

To cascade multiple AS1109 devices, pin SDO must be connected to pin SDI of the next AS1109 (see Figure 23). At each rising edge of CLK the LSB of the shift register will be written into the shift register SDI of the next AS1109 in the chain. Data at the SDI pin is clocked in at the rising edge of the CLK pulse and is clocked out at the SDO pin 8.5 clock cycles later at the falling edge of the CLK pulse.

**Note:** When  $n^*$ AS1109 devices are in one chain,  $n^*$ 8 clock pulses are needed to latch-in the input data.

Figure 23. Cascading AS1109 Devices

#### **Constant Current**

In LED display applications, the AS1109 provides virtually no current variations from channel-to-channel and from AS1109-to-AS1109. This is mostly due to 2 factors:

- While Iout ≥ 50mA, the maximum current skew is less than ±2% between channels and less than ±2% between AS1109 devices.

- In the saturation region, the characteristics curve of the output stage is flat (see Figure 5 on page 7). Thus, the output current can be kept constant regardless of the variations of LED forward voltages (VF).

### **Adjusting Output Current**

The AS1109 scales up the reference current (IREF) set by external resistor (REXT) to sink a current (IOUT) at each output port. As shown in Figure 3 on page 7 the output current in the saturation region is extremely flat so that it is possible to define it as target current (IOUT TARGET). IOUT TARGET can be calculated by:

$$VREXT = 1.253V (EQ 1)$$

$$IREF = VREXT/REXT$$

(if the other end of REXT is connected to ground) (EQ 2)

IOUT TARGET =

$$IREF^*15 = (1.253V/Rext)^*15$$

(EQ 3)

#### Where:

REXT is the resistance of the external resistor connected to pin REXT.

VREXT is the voltage on pin REXT.

The magnitude of current (as a function of REXT) is around 100mA at  $186\Omega$ , 50.52mA at  $372\Omega$  and 25.26mA at  $744\Omega$ . Figure 3 on page 7 shows the relationship curve between the IOUT TARGET of each channel and the corresponding external resistor (REXT).

### **Package Power Dissipation**

The maximum allowable package power dissipation (PD) is determined as:

$$PD(MAX) = (TJ-TAMB)/RTH(J-A)$$

(EQ 4)

When 8 output channels are turned on simultaneously, the actual package power dissipation is:

$$PD(ACT) = (IDD*VDD) + (IOUT*Duty*VDS*8)$$

(EQ 5)

Therefore, to keep PD(ACT) ≤ PD(MAX), the allowable maximum output current as a function of duty cycle is:

$$IOUT = \{[(T_J - T_{AMB})/RTH(J - A)] - (IDD*VDD)\}/VDS/Duty/8$$

(EQ 6)

#### Where:

$T_{J} = 150^{\circ}C$

#### **Delayed Outputs**

The AS1109 has graduated delay circuits between outputs. These delay circuits can be found between  $OUTN_n$  and constant current block.

The fixed delay time is 20 ns (typ) where OUTN0 has no delay, OUTN1 has 20ns delay, OUTN2 has 40ns delay ... OUTN7 has 140ns delay. This delay prevents large inrush currents, which reduce power supply bypass capacitor requirements when the outputs turn on (see Figure 12 on page 10)

### **Switching-Noise Reduction**

LED drivers are frequently used in switch-mode applications which normally exhibit switching noise due to parasitic inductance on the PCB.

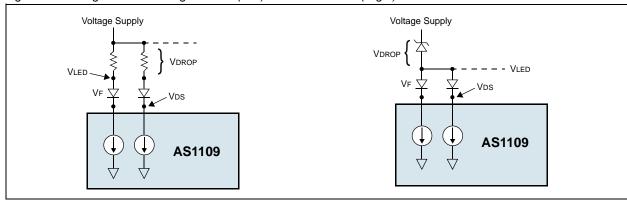

### **Load Supply Voltage**

Considering the package power dissipation limits (see EQ 4:6), the AS1109 should be operated within the range of Vps = 0.4 to 1.0V.

For example, if VLED is higher than 5V, VDS may be so high that PD(ACT) > PD(MAX) where VDS = VLED - VF. In this case, the lowest possible supply voltage or a voltage reducer (VDROP) should be used. The voltage reducer allows VDS = (VLED - VF) - VDROP.

Note: Resistors or zener diodes can be used as a voltage reducer as shown in Figure 24.

Figure 24. Voltage Reducer using Resistor (Left) and Zener Diode (Right)

## 10 Package Drawings and Markings

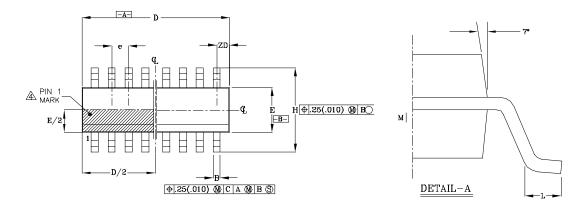

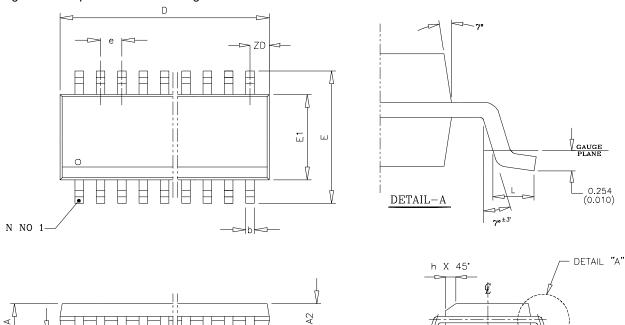

The device is available in an 16-pin SOIC-150 package.

Figure 25. 16-pin SOIC-150 Package

#### Notes:

- 1. Lead coplanarity should be 0 to 0.10mm (.004") max.

- 2. Package surfacing:

- a. Top: matte (charmilles #18-30).

- b. All sides: matte (charmilles #18-30).

- c. Bottom: smooth or matte (charmilles #18- 30).

- 3. All dimensions excluding mold flashes and end flash from the package body shall not exceed 0.25mm (.010") per side (D).

- 4. Detail of pin #1 identifier are optional but must be located within the zone indicated.

- 5. Dimensions are in millimeters.

| Symbol | Min      | Max  |

|--------|----------|------|

| A1     | 0.10     | 0.25 |

| В      | 0.36     | 0.46 |

| С      | 0.19     | 0.25 |

| D      | 9.80     | 9.98 |

| Е      | 3.81     | 3.99 |

| е      | 1.27     | BSC  |

| Н      | 5.80     | 6.20 |

| h      | 0.25     | 0.50 |

| L      | 0.41     | 1.27 |

| Α      | 1.52     | 1.72 |

| α      | 00       | 8°   |

| ZD     | 0.51 REF |      |

| A2     | 1.37     | 1.57 |

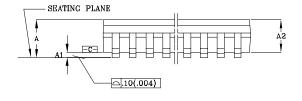

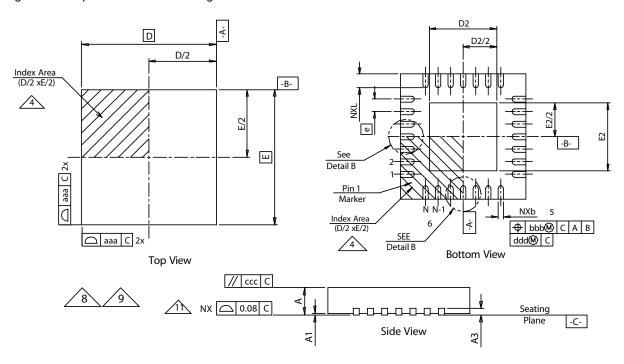

Figure 26. 16-pin SSOP-150 Package

| Symbol | Min       | Max  |  |

|--------|-----------|------|--|

| Α      | 1.35      | 1.75 |  |

| A1     | 0.10      | 0.25 |  |

| A2     | 1.37      | 1.57 |  |

| b      | 0.20      | 0.30 |  |

| С      | 0.19      | 0.25 |  |

| D      | 4.80      | 4.98 |  |

| Е      | 5.79      | 6.20 |  |

| E1     | 3.81      | 3.99 |  |

| е      | 0.635     | BSC  |  |

| h      | 0.22      | 0.49 |  |

| L      | 0.40      | 1.27 |  |

| θ      | 00        | 80   |  |

| ZD     | 0.230 REF |      |  |

| N      | 16 pins   |      |  |

#### Notes:

- 1. Lead coplanarity should be 0 to 0.10mm (.004") max.

- 2. Package surfacing:

- a. Top: matte (charmilles #18-30).

- b. All sides: matte (charmilles #18-30).

- c. Bottom: smooth or matte (charmilles #18-30).

- 3. All dimensions excluding mold flashes and end flash from the package body shall not exceed 0.25mm (.010") per side (D).

- 4. Dimensions "b" does not include dambar protrusion/intrusion but solder coverage.

- 5. Dimensions are in millimeters.

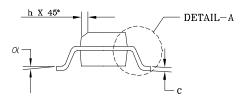

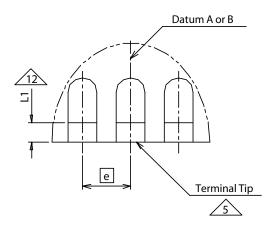

Figure 27. 16-pin QFN 4x4mm Packages

| 16-pin QFN 4x4mm Dimensions |      |             |      |          |  |

|-----------------------------|------|-------------|------|----------|--|

| Symbol                      | Min  | Nom         | Max  | Notes    |  |

| aaa                         |      | 0.15        |      | 1, 2     |  |

| bbb                         |      | 0.10        |      | 1, 2     |  |

| ccc                         |      | 0.10        |      | 1, 2     |  |

| ddd                         |      | 0.05        |      | 1, 2     |  |

| b                           | 0.25 | 0.30        | 0.35 | 1, 2     |  |

| е                           |      | 0.65        |      |          |  |

| Α                           | 0.70 | 0.75        | 0.80 | 1, 2     |  |

| A1                          | 0.00 | 0.02        | 0.05 | 1, 2     |  |

| А3                          |      | 0.20<br>REF |      | 1, 2     |  |

| L1                          | 0.03 |             | 0.15 | 1, 2     |  |

| D BSC                       |      | 4.00        |      | 1, 2, 10 |  |

| E BSC                       |      | 4.00        |      | 1, 2, 10 |  |

| D2                          | 2.00 | 2.15        | 2.25 | 1, 2, 10 |  |

| E2                          | 2.00 | 2.15        | 2.25 | 1, 2, 10 |  |

| L                           | 0.45 | 0.55        | 0.65 | 1, 2, 10 |  |

| N                           |      | 16          |      | 1, 2, 10 |  |

| ND                          |      | 4           |      | 1, 2, 10 |  |

| NE                          |      | 4           |      | 1, 2, 10 |  |

Odd Terminal Side

#### Notes:

- 1. Dimensioning and tolerancing conform to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters; angles in degrees.

- 3. N is the total number of terminals.

- 4. The terminal #1 identifier and terminal numbering convention shall conform to *JEDEC 95 SPP-012*. Details of terminal #1 identifier are optional but must be located within the zone indicated. The terminal #1 identifier may be either a mold or marked feature.

- 5. Dimension b applies to metallized terminal and is measured between 0.15 and 0.30mm from terminal tip. If one end of the terminal has the optional radius, the b dimension should not be measured in that radius area.

- 6. Dimensions ND and NE refer to the number of terminals on each D and E side, respectively.

- 7. Depopulation is possible in a symmetrical fashion.

- 8. Figure 27 is shown for illustration only and does not represent any specific variation.

- 9. All variations may be constructed per Figure 27, however variations may alternately be constructed between square or rectangle shape per dimensions D and E.

- 10. Refer to the Dimensions Table for a complete set of dimensions.

- 11. Bilateral coplanarity zone applies to the exposed heat sink slug as well as the terminals.

- 12. Depending on the method of lead termination at the edge of the package, pullback (L1) may be present. L minus L1 to be ≥ 0.33mm.

# 11 Ordering Information

The device is available as the standard products shown in Table 9.

Table 9. Ordering Information

| Туре        | Description                                         | Delivery Form | Package            |

|-------------|-----------------------------------------------------|---------------|--------------------|

| AS1109-BSOU | Constant-Current, 8-Bit LED Driver with Diagnostics | Tubes         | 16-pin SOIC-150    |

| AS1109-BSOT | Constant-Current, 8-Bit LED Driver with Diagnostics | Tape and Reel | 16-pin SOIC-150    |

| AS1109-BSSU | Constant-Current, 8-Bit LED Driver with Diagnostics | Tubes         | 16-pin SSOP-150    |

| AS1109-BSST | Constant-Current, 8-Bit LED Driver with Diagnostics | Tape and Reel | 16-pin SSOP-150    |

| AS1109-BQFR | Constant-Current, 8-Bit LED Driver with Diagnostics | Tray          | 16-pin QFN (4x4mm) |

| AS1109-BQFT | Constant-Current, 8-Bit LED Driver with Diagnostics | Tape and Reel | 16-pin QFN (4x4mm) |

All devices are RoHS compliant and free of halogene substances.

### Copyrights

Copyright © 1997-2009, austriamicrosystems AG, Schloss Premstaetten, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### **Disclaimer**

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

#### **Headquarters**

austriamicrosystems AG A-8141 Schloss Premstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact-us